# 80C51 family EPROM products

### **EPROM PRODUCTS**

## **Programming the 87C51**

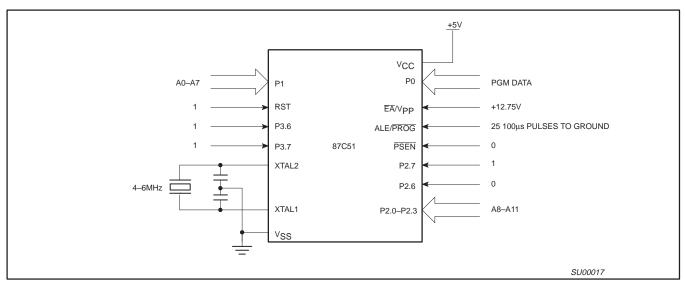

The setup for programming the microcontroller is shown in Figure 1. Note that the part is running with a 4 to 6 MHz oscillator. The clock must be running because the device is executing internal address and program data transfers during the programming.

To program the 87C51, the address of the EPROM location to be programmed is applied to ports 1 and 2 as shown in Figure 1. The code byte to be programmed into this location is applied to port 0. RST,  $\overline{\text{PSEN}}$ , and the pins of ports 2 and 3 specified in Table 1 are held at the "Program Code Data" levels specified in the table. The ALE/PROG is then pulsed low 25 times to program the addressed location.

### **Encryption Table**

The encryption table is a feature of the 87C51, and its derivatives, that protects the code from being easily read by anyone other than the programmer. The encryption table is 16 to 64 bytes of code, depending on the microcontroller, that are exclusive NORed with the program code data as it is read out. The first byte is XNORed with the first location read, the second with the second read, etc. through the sixteenth byte read. The seventeenth byte is XNORed with the

first byte of the encryption table, the eighteenth with the second, etc. and on in sixteen-byte groups.

After the Encryption table has been programmed the user has to know its contents in order to correctly decode the program code data. The encryption table itself cannot be read out.

The encryption table is programmed in the same manner as the program memory, but using the "Pgm Encryption Table" levels specified in Table 1. After the encryption table is programmed, verification cycles will produce only encrypted information.

### **Security Bit**

There are two security bits on the 87C51 that, when set, prevent the program data memory from being read out or programmed further. To program the security bits, repeat the programming sequence using the "Pgm Security Bit" levels specified in Table 1.

After the first security bit is programmed, further programming of the code memory or the encryption table is disabled. The other security bit can of course still be programmed. With only security bit one programmed, the memory can still be read out for program verification. After the second security bit is programmed, it is no longer possible to read out (verify) the program memory.

Figure 1. Programming Configuration

1998 Jan 06

| MODE                 | RST | PSEN | ALE/PROG | EA/V <sub>PP</sub> | P2.7 | P2.6 | P3.7 | P3.6 |

|----------------------|-----|------|----------|--------------------|------|------|------|------|

| Read signature       | 1   | 0    | 1        | 1                  | 0    | 0    | 0    | 0    |

| Program code data    | 1   | 0    | 0*       | V <sub>PP</sub>    | 1    | 0    | 1    | 1    |

| Verify code data     | 1   | 0    | 1        | 1                  | 0    | 0    | 1    | 1    |

| Pgm encryption table | 1   | 0    | 0*       | $V_{PP}$           | 1    | 0    | 1    | 0    |

| Pgm security bit 1   | 1   | 0    | 0*       | $V_{PP}$           | 1    | 1    | 1    | 1    |

| Pgm security bit 2   | 1   | 0    | 0*       | $V_{PP}$           | 1    | 1    | 0    | 0    |

Table 1. EPROM Programming Modes

#### NOTES:

- 1. "0" = valid low for that pin, "1" = valid high for that pin.

- 2.  $V_{PP} = 12.75 \pm 0.25 V.$

- 3.  $V_{CC} = 5V \pm 10\%$  during programming and verification.

- \* ALE/PROG receives 25 programming pulses while V<sub>PP</sub> is held at 12.75V. Each programming pulse is low for 100ms (±10μs) and high for a minimum of 10μs.

Figure 2. Program Verification

### **Program Verification**

If security bit 2 has not been programmed the on-chip program memory can be read out for program verification. To verify the contents of the program memory, the address of the location to be read is applied to ports 1 and 2 as shown in Figure 2. The other pins are held at the "Verify Code Data" levels indicated in Table 1. The contents of the addressed location will appear on port 0. For this operation external pull-ups are required on port 0 as shown in Figure 2. Note that if the encryption table has been programmed the data presented at port 0 will be the exclusive NOR of the program byte with a byte from the encryption table.

## Signature Bytes

The 87C51 contains two signature bytes that can be read and used by an EPROM programming system to identify the device. The signature bytes identify the device as an 87C51 manufactured by Philips.

The signature bytes are read by the same procedure as a normal verification of locations 030H and 031H, except that P3.6 and P3.7 need to be pulled to a logic low.

## Programming the 87C750, 87C751 and 87C752

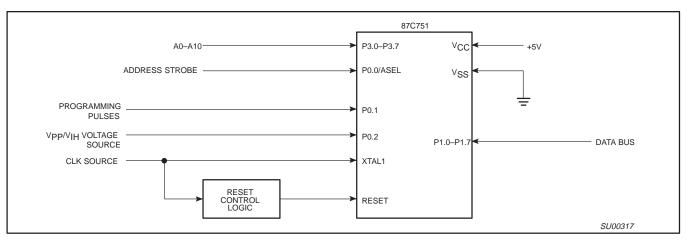

The 87C750, 87C751 and 87C752 are programmed using a Quick-pulse programming algorithm that is similar to that used for the 87C51. It differs from the 87C51 in that a serial data stream is used to place the 87C751 in the programming mode.

Figure 3 shows a block diagram of the programming configuration for the 87C751. Port pin P0.2 is used for the programming voltage supply input ( $V_{PP}$  signal). Port pin P0.1 is used for the program (PGM) signal.

Port 3 accepts the address input for the EPROM location to be programmed. Both the high and low components of the eleven-bit address are presented to the part through port 3. Multiplexing of the address components is performed using ASEL (P0.0).

Port 1 is used as a bidirectional data bus during programming and verify operations. During the programming mode, it accepts the byte to be programmed. In the verify mode, it returns the contents of the specified address location.

The X1 pin is the oscillator input and receives the master system clock. This clock should be between 1.2 and 6MHz.

1998 Jan 06 2

# 80C51 family EPROM products

The RESET pin is used to accept the serial data stream that places the 87C751 into various programming modes. This pattern consists of a 10-bit code with the LSB send first. Each bit is synchronized to the clock input X1.

To program the 87C751 the part must be put into the programming mode by presenting the proper serial code (see Table 2) to the RESET pin. To do this RESET should be held high for at least two machine cycles. Port pins P0.1 and P0.2 will be at VOH as a result of this, but they must be driven high prior to sending the serial data stream on the RESET pin. The serial data bits can now be transmitted over the RESET pin placing the 87C751 into one of the programming modes. Following the transmission of the last data bit, the reset pin should be held low.

Next the address information for the location to be programmed is placed on Port 3 and ASEL is used to perform the address multiplexing. ASEL should be driven high and then Port 3 driven with the high-order address bits. ASEL is then driven low, latching the high-order bits internally. Port 3 can now be driven with the low 8 bits of the address, completing the addressing of the location to be programmed.

A high-voltage  $V_{PP}$  level is now applied to the  $V_{PP}$  input. This sets Port 1 as an input port. The data to be programmed to the EPROM array should be placed on Port 1. A series of 25 programming pulses is now applied to the PGM pin (P0.1) to program the addressed EPROM location.

Figure 3. Programming Configuration

Table 2. 87C750, 87C751, and 87C752 Serial Codes

| OPERATION              | SERIAL CODE | P0.1 (PGM/)     | P0.2 (V <sub>PP</sub> ) |

|------------------------|-------------|-----------------|-------------------------|

| Program user EPROM     | 296H        | _*              | V <sub>PP</sub>         |

| Verify user EPROM      | 296H        | V <sub>IH</sub> | V <sub>IH</sub>         |

| Program key EPROM      | 292H        | _*              | $V_{PP}$                |

| Verify key EPROM       | 292H        | V <sub>IH</sub> | V <sub>IH</sub>         |

| Program security bit 1 | 29AH        | _*              | $V_{PP}$                |

| Program security bit 2 | 298H        | _*              | $V_{PP}$                |

| Verify security bits   | 29AH        | V <sub>IH</sub> | V <sub>IH</sub>         |

| Read signature bytes   | 294H        | V <sub>IH</sub> | V <sub>IH</sub>         |

### NOTE:

1998 Jan 06 3

$<sup>^{\</sup>ast}$   $\,$  Pulsed from  $V_{IH}$  to  $V_{IL}$  and returned to  $V_{IH.}$

# 80C51 family EPROM products

### **Program Verification**

The EPROM array can be verified by placing the part in the programming mode as described above and forcing the  $V_{PP}$  pin to the  $V_{OH}$  level. Four machine cycles after addressing a location the contents of the addressed location will appear on Port 1.

## 87C750, 87C751 and 87C752 Signature Bytes

The signature bytes for the 87C750, 87C751 and 87C752 are read differently and are in different locations than those on the 87C51. Due to its reduced pin count, the part has to be put into "Signature Byte Read Mode" by placing a 10-bit serial data stream on the Reset pin. The proper code and the conditions of P0.1 and P0.2, for this mode, are shown in Table 2.

Once the part has been placed into the Signature Byte Read Mode, the signature bytes can be read by the same procedure as a normal verification of locations 01EH and 01FH. The values are:

01EH = 15H indicates the part is made by Philips

01FH = 91H - 87C751 01FH = 95H - 87C752

## **Programming Features**

The 87C751 has all of the special programming features incorporated within its EPROM array that the 87C51 has. It has an encryption key table and two security bits. These function exactly as they do in the 87C51. They are programmed or verified by sending the proper code over the RESET pin (see Table 2) and then following the 87C751 programming procedure as described previously.

1998 Jan 06 4